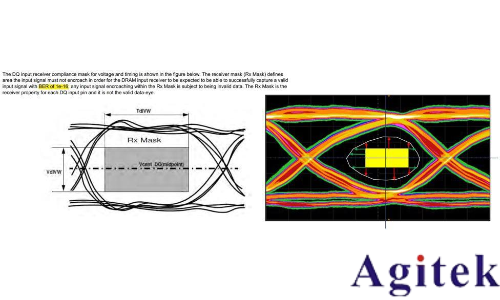

对于 DDR 源同步操作,必然要求DQS 选通信号与 DQ 数据信号有一定建立时间 tDS 和保持时间 tDH 要求,否则会导致接收锁存信号错误,DDR4 信号速率达到了3.2GT/s,单一比特位宽仅为 312.5ps,时序裕度也变得越来越小,传统的测量时序的方式在短时间内的采集并找到 tDS/tDH 最差值,无法大概率体现由于 ISI 等确定性抖动带来的对时序恶化的贡献,也很难准确反映随机抖动 Rj 的影响。在 DDR4 的眼图分析中就要考虑这些抖动因素,基于双狄拉克模型分解抖动和噪声的随机性和确定性成分,外推出基于一定误码率下的眼图张度。JEDEC 协会在规范中明确了在 DDR4 中测试误码率为 1e-16 的眼图轮廓,确保满足在 Vcent 周围Tdivw 时间窗口和 Vdivw 幅度窗口范围内模板内禁入的要求。

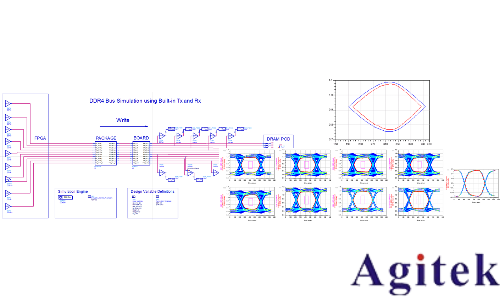

是德科技 ADS 仿真软件的 DDR4 总线仿真器,提供了统计眼图分析的功能,能够在短时间内统计计算在极低误码率(1e-16)下的 DQ 眼图,根据规范判断模板是否违规。另外基于总线的仿真,也很易于仿真基于串扰因素下的眼图质量。

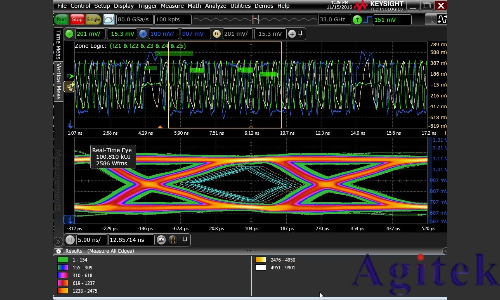

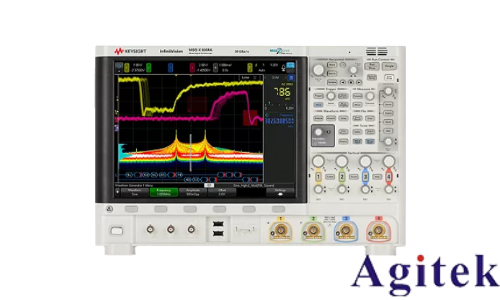

基于示波器的 DDR4 信号实测,可以利用大家熟悉的 InfiniiScan 区域触发功能,很容易分离出“写”信号,再通过 Gating 功能对Burst 写信号做时钟恢复和眼图重建,再进行 Eye Contour 测量,并验证 1e-16 误码率下的眼图模板是否违规。如果是使用一致性测试软件,就不用手动操作,软件会自动跟踪和分离波形并实现眼图测试(如下图所示)

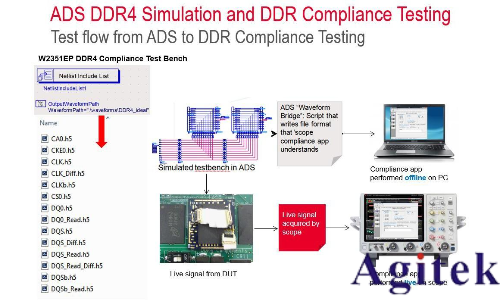

在早期设计阶段,如何完整评价 DDR 信号质量和时序等参数呢,这里为大家介绍一个设计到验证的流程。ADS 提供了W2351EP DDR4 一致性分析工具,在ADS 仿真后,生成波形可以直接导入到运行于电脑里的示波器离线分析软件 Infiniium 和N6462A DDR4/LPDDR4 一致性测试套件,这个软件可以分析前面所说的 JEDEC 对DDR4 信号要求的电气和时序等参数,判断是否符合规范要求,以测试报告形式呈现,这种方式可以在设计阶段发现违规问题,及时改进设计,缩短研发周期,降低硬件开发成本。另一方面,在硬件已经打板回来,可以通过 V 系列等示波器测试信号,通过实际的信号检查存在的问题,将仿真的结果和实际测试的结果做相关对比,进一步迭代优化仿真模型和测量方法,使仿真和测试结果逐渐逼近。

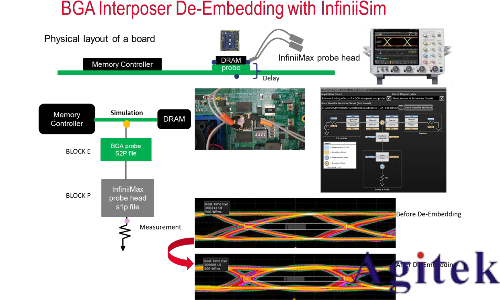

DDR4 做测试时,由于 BGA 信号难以探测,是德科技提供了 N2114A/N2115A 等DDR4 Interposer,将 BGA 下方的信号引到 Interposer 外围,方便探头焊接,为了减少 Interposer 对信号带来影响,在 interposer 内专门有埋阻设计,减少由于分支和走线带来的阻抗不连续和对信号的负载效应;但为了精确测量,我们需要对 BGA Interposer 带来的误差进行修正。可以通过 InfiniiSim 或在 DDR4 一致性测试软件N6462A 内进行去嵌,在软件内使用多端口拓扑模型,载入 Interposer 的S 参数,生成从探头测试点到 BGA 焊球位置的去嵌传递函数,在示波器中测得去嵌后的波形,下图可以看到去嵌后信号眼图的改善。

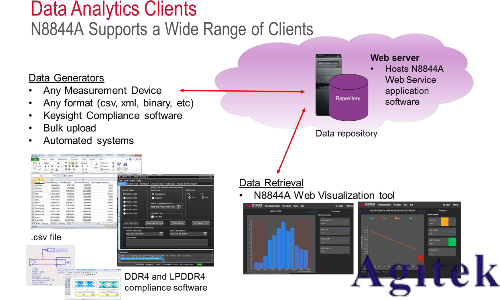

最后,对于物理层无论是仿真还是一致性测试软件得到的数据,都可以通过数据分析工具 N8844A 导入到云端,通过可视化工具,生成统计分析表格,对比性分析高低温、高低电压等极端情况下不同的测试结果,比较不同被测件异同。为开发测试部门提供灵活和有效的大数据分析平台。

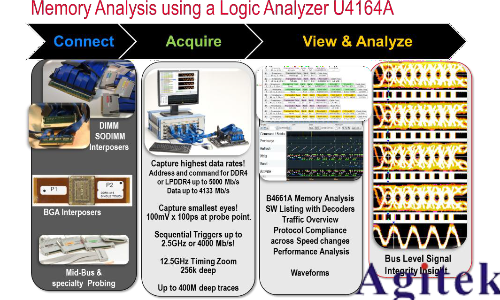

除了在物理层信号质量和基本时序参数之外,DDR 总线的状态机复杂时序特性,以及总线的命令操作解析需要通过逻辑分析仪辅助分析。是德科技的U4164A 逻辑分析

仪,同步分析速率可以达到 4Gbps,采样窗口可以低至 100mv x 100ps,单路采集样本高达 400M,对于 DDR4 的测试是非常合适的,另外配合 B4661A memory 分析软件,可以解析 DDR4 会话操作,实现 DDR4 总线的命令解码,解析 MRS,命令,行列地址,并可以直接触发物理地址捕获特定信号,利用深存储的大量样本,可以对DDR 总线的性能进行分析,包括统计内存总线有效吞吐速率,统计各种命令操作以及总线利用率,分析对不同内存地址空间的访问效率。另外利用是德科技独有的逻辑分析仪内部眼图扫描功能,可以同时分析扫描总线各个比特位的眼图质量。

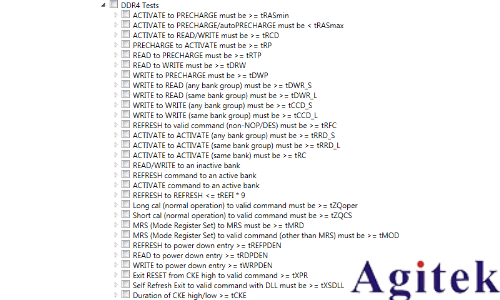

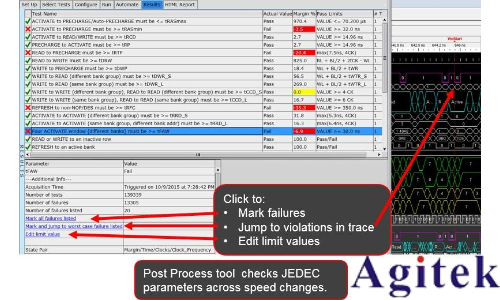

JEDEC 的规范中,定义了如下这些参数要求,B4661A 软件可以支持这些参数的实时和后分析功能,分析判断测试结果是否符合规范的范围要求,并且可以跟踪测量结果,对于违规的测量参数可以跟踪到波形界面,从而定位命令和操作的根源问题。

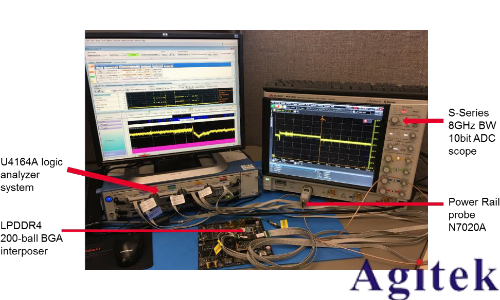

以上,我们介绍了 DDR4 总线物理层仿真测试和协议层的测试方案,借助仿真软件、示波器和逻辑分析仪对DDR4 总线分析调试的主要方法。对于 DDR 系统中存在的复杂问题,还可以使用逻辑分析仪和示波器进行联合调试,逻辑分析仪优势在解析 DDR 总线会话和操作性能分析,示波器的强大在于信号波形的观测,也可以测量电源纹波和噪声。是德科技的逻辑分析仪自带的 View Scope 功能,可以通过网线和触发线, 同步捕获示波器内的波形,时基相关的查看逻辑操作和物理波形的关系,下面的实测场景就是使用逻辑分析仪捕获LPDDR4信号,使用 10 比特的 S 示波器配合电源完整性测试探头 N7020A,精确观测供电电压 1.1V 的实例,可以看到在逻辑分析仪界面, 电源电压轨迹展开出现尖峰和跌落。

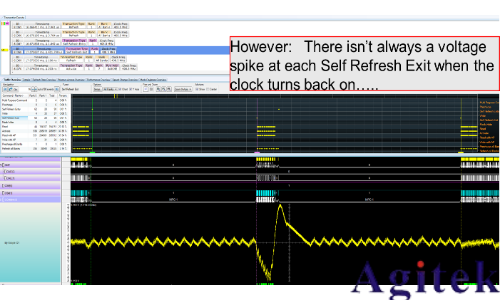

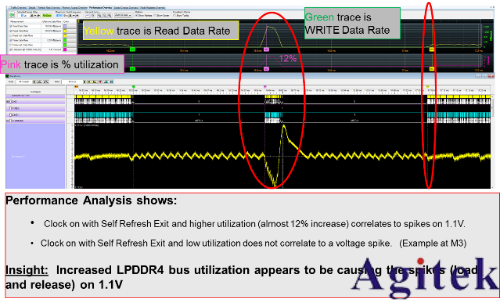

再通过逻辑分析仪的内存软件解析 DDR 总线的操作和分析性能,可以分析出由于系统中集中的读操作,以及LPDDR4的速率切换导致了电源电压的波动,以及特定命令操作导致的电压跌落现象,下图我们展示了逻辑分析仪界面内总线会话解码、总线利用率时域统计和电压波形的同步显示,展开命令后可以发现在电压出现尖峰的周边是Clock 重新打开、Self Refresh Exit 操作,再看总线利用率的时域变化,突发的读操 作总线利用率提升了 12%,由于突发的连续读操作形成电源负载瞬间变化,导致 1.1 V

上出现了瞬间的 38 mV 的尖峰。这个电压波动可能导致系统工作可靠性下降,所以需要进一步改善 DDR 供电电源网络的设计。

相关产品

是德HD304MSO示波器提供14位ADC、4个模拟通道、100 Mpts存储器、1,300,000 wfms/s更新速率和10.1英寸电容式触摸屏。 亮

是德HD302MSO InfiniiVision示波器特点 HD302MSO示波器提供14位ADC、2个模拟通道、100 Mpts存储器、1,300,00

Keysight UXR1102B示波器性能特点: 带宽:110 GHz 通道数:2通道,可升级至4通道 存储器深度:每通道500 Mpts,可升级至

是德N2140A高阻无源探头是一款具有以下特点的测试设备: 1.高带宽:该探头可以实现直流至200MHz的带宽,适用于高频率的测试需求。 2.长电缆:探

相关文章

在使用是德科技(Keysight Technologies)示波器进行电子测量时,若出现“无信号显示”的情况,可能由多种原因导致。为确保测量工作顺利进行,需系统性地排查故障源,从信号链路的各个环节入手,逐步定位并解决问题。

在现代电子测量中,示波器作为分析信号时域特性的核心工具,其存储深度(也称记录长度)直接影响波形捕获的精度与时间跨度。对于是德科技(Keysight)示波器而言,合理设置长存储深度,不仅能完整捕获长时间的动态信号,还能保留高频细节,避免混叠与数据丢失,是实现高精度测量的关键环节。

随着工业自动化与新能源技术的快速发展,电机驱动系统的复杂性日益提升,对其控制精度与稳定性的测试要求也不断提高。在这一背景下,示波器作为核心测试工具,承担着信号观测、故障诊断与性能优化的重要任务。是德科技(Keysight)凭借其先进的示波器产品线,在电机驱动测试中展现出卓越的技术优势与广泛的应用价值。

在现代电子系统中,电源噪声是影响电路稳定性与信号完整性的关键因素之一。随着数字器件工作电压不断降低、电流需求持续升高,对电源完整性的要求日益严苛。是德示波器凭借其强大的快速傅里叶变换(FFT)功能,为电源噪声的精准分析提供了高效的频域视角,帮助工程师从时域难以察觉的微弱干扰中定位问题根源。

是德科技(Keysight)示波器作为电子测试领域的主流设备,广泛应用于研发、教育及工业检测场景。为满足不同用户需求,其多数型号支持多语言界面切换,尤其对中文用户的本地化体验进行了优化。掌握中英文界面的灵活切换方法,不仅能提升操作效率,也便于团队协作与跨国交流。

联系电话: 18165377573